SoMs Power Architecture

# miriac® MPX2041 (EOL)

System on Module based on NXP® QorIQ® P2041 CPU

## Highlights

- up to 4 GB DDR3 memory, 64-bit with EEC, soldered

- 10x @ 5 GHz SerDes lanes offer a completely new performance range for demanding I/O functions

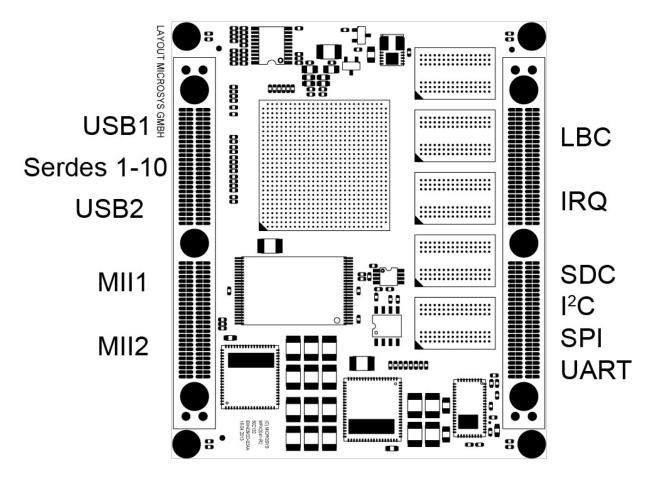

- two 208 Pin Zero Force Connectors, that make all I/O and bus signals available to the carrier board

- High precision RTC

- Power: 3.3 V DC single supply, 24 A core voltage regulator

## **Product Description**

The miriac® MPX2041 CPU Module is the first Quad Core QorlQ® based SoM by MicroSys.

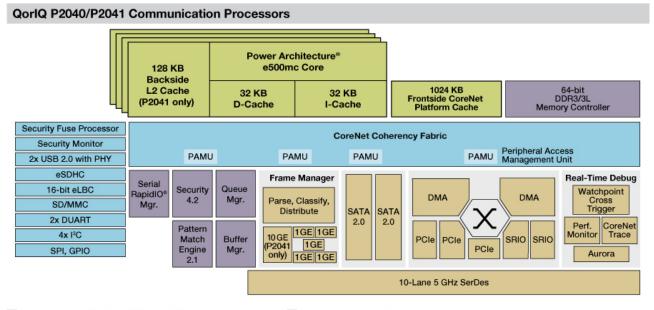

The four e500mc CPU cores in combination with the integrated hardware hypervisor and CoerNet fabric allow completely new designs for control applications. The CoreNet fabric eliminates internal data exchange bottlenecks between the CPU cores. This offers higher performance and safer operation on application level.

| Features              |                                                                                               |

|-----------------------|-----------------------------------------------------------------------------------------------|

| CPU                   |                                                                                               |

| Architecture:         | PowerPC                                                                                       |

| Processor:            | NXP® QorIQ® P2041 CPU                                                                         |

|                       | 4x e500mc cores up to 1.5 GHz, 32 kB I/D Cache and 128 kB L2 Cache per core                   |

|                       | 1 MB CoreNet platform cache with EEC                                                          |

| Memory                |                                                                                               |

| Flash:                | up to 512 MB NAND Flash                                                                       |

| Flash Card:           | 1x SD/MMC                                                                                     |

| High Speed IO         |                                                                                               |

| SerDes lanes:         | high speed interfaces supporting various multiplexed options by 10 SerDes lanes @ 5 GHz, e.g. |

|                       | - 2x SATA                                                                                     |

|                       | - 3x PCI Express®                                                                             |

|                       | - 2x SRIO or                                                                                  |

|                       | - 4x SGMII                                                                                    |

| USB 2.0:              | 2x USB 2.0                                                                                    |

| Operating Condition   |                                                                                               |

| Temperature:          | optional: ext. temp.                                                                          |

| Mechanical            |                                                                                               |

| Formfactor:           | MPX-1, 77 mm x 66 mm                                                                          |

| Software / Additional |                                                                                               |

| Software Support:     | Linux                                                                                         |

|                       | Microware OS-9                                                                                |

|                       | VxWorks                                                                                       |

|                       | MicroC/OS-II                                                                                  |

### QNX

#### others are avialable on request

#### General Note:

Our standard product versions offer what we consider to be the optimum configuration in terms of performance, price, usage and TDP. The product features lists specify the maximum range of functions per interface. However, not all interfaces or functions are always available in parallel. Flexible SERDES multiplexing is one of the reasons for this. In addition, we provide multiple memory expansion options and are also happy to accommodate specific customer wishes. So do not hesitate to <u>contact us</u> directly to discuss your desired configuration.

Core Complex (CPU, L2 and Frontside CoreNet Platform Cache) 🔲 Basic Peripherals and Interconnect

Accelerators and Memory Control Networking Elements

NXP® QorlQ® P2040, P2041

NXP® QorlQ® P2040, P2041

Mühlweg 1 82054 Sauerlach Germany Sales: +49 8104 801-130 E-Mail: info@microsys.de www.microsys.de

MicroSys, due to constant technical development, reserves the right to change this datasheet and product without prior notice. All data is for information purpose only. MicroSys excludes its liability for the accuracy and completeness of information as well as for the intended use. No kind of guarantee is granted by MicroSys. Rev. 27.07.2024